Metric Description

A pipeline slot represents hardware resources needed to process one uOp.

The Top-Down Characterization assumes that for each CPU core, on each clock cycle, there are several pipeline slots available. This number is called Pipeline Width.

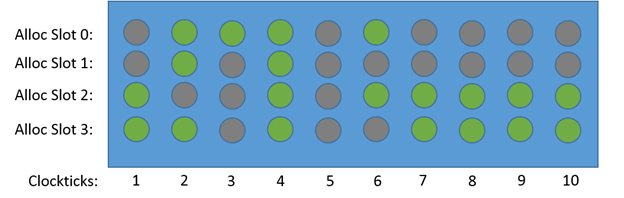

In the example below, there is a 4-wide CPU that executes code for 10 clock cycles:

In this example, there are 40 Pipeline Slots (4 * 10). If a Pipeline Slot does not retire, a uOp is attributed to a Stall.

In the next example, 20 out of 40 slots are stalled (did not retire a uOp). This means that the code efficiency from the microarchitecture perspective is only 50%:

The Top-Down metrics measured in Pipeline Slots, for example, Front-End Bound and Back-End Bound, measure a percentage of Pipeline Slots stalled due to the reason specified by the metrics such as Front-End issues and Back-End issues.